# 3C90xC NICs Technical Reference

3Com® EtherLink® and EtherLink Server 10/100 PCI network interface cards

Part Number: 89-0931-000 Published September1999

3Com Corporation 5400 Bayfront Plaza Santa Clara, California 95052-8145 Copyright © 3Com Corporation, 1998. All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without permission from 3Com Corporation.

3Com Corporation reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of 3Com Corporation to provide notification of such revision or change.

3Com Corporation provides this documentation without warranty of any kind, either implied or expressed, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. 3Com may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

#### **UNITED STATES GOVERNMENT LEGENDS:**

If you are a United States government agency, then this documentation and the software described herein are provided to you subject to the following restricted rights:

#### For units of the Department of Defense:

Restricted Rights Legend: Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) for Restricted Rights in Technical Data and Computer Software Clause at 48 C.F.R. 52.227-7013. 3Com Corporation, 5400 Bayfront Plaza, Santa Clara, California 95052-8145.

#### For civilian agencies:

Restricted Rights Legend: Use, reproduction, or disclosure is subject to restrictions set forth in subparagraph (a) through (d) of the Commercial Computer Software – Restricted Rights Clause at 48 C.F.R. 52.227-19 and the limitations set forth in 3Com Corporation's standard commercial agreement for the software. Unpublished rights reserved under the copyright laws of the United States.

If there is any software on removable media described in this documentation, it is furnished under a license agreement included with the product as a separate document, in the hard copy documentation, or on the removable media in a directory file named LICENSE.TXT. If you are unable to locate a copy, please contact 3Com and a copy will be provided to you.

Unless otherwise indicated, 3Com registered trademarks are registered in the United States and may or may not be registered in other countries.

3Com and EtherLink are registered trademarks of 3Com Corporation. Lanworks is a trademark of 3Com Corporation.

Magic Packet is a trademark of Advanced Micro Devices, Inc. Atmel is a trademark of Atmel Corporation. Broadcom is a trademark of Broadcom Corporation. Dell is a registered trademark of Dell Computer Corporation. IBM is a registered trademark of International Business Machines Corporation. Lucent Technologies is a trademark of Lucent Technologies, Inc. National Semiconductor is a registered trademark of National Semiconductor Corporation.

Other brand and product names may be registered trademarks or trademarks of their respective holders.

## **CONTENTS**

INTRODUCTION

3C90xC NIC Features

Data Structure Lists 25 PCI Bus Master Operation

**PCI Memory Commands**

PCI Bus Request Control

25

25

About This Technical Reference

1

#### Terms and Acronyms 15 Register Bit Maps 17 ARCHITECTURE 3C90xC NIC Block Diagram 18 ASICs 18 Hardware Identification 19 Software Identification ASIC Block Descriptions PCI Bus Controller 19 Upload and Download Engines 19 Transmit and Receive FIFOs 19 10/100 Mbps Ethernet MAC Management Statistics Auto-Negotiation 20 10/100 Mbps PHY Keep-Alive 20 Wake Event 20 SOS Connector 20 SMBus Connector **RWU Connector** 21 Other NIC Devices BIOS ROM 21 Serial EEPROM 21 Host Registers 21 Bit Widths of Register Accesses 22 Command Register 22 Interrupt Status Register 3C90xC NIC Register Layout 22 **OPERATION**

```

Download

26

Upload

27

Power Management 27

Power Up Sequencing

Low-power Mode

Power States 27

29

Power Management Registers

PowerMgmtCap

PowerMgmtCtrl

PowerMgmtEvent 31

Remote Wake-Up

Wake-up Packets 32

Downloading Wake-up Frame Patterns

Wake-up Frame Patterns

Magic Packet Technology

Change of Link State

Wake-on-Timer 35

WakeOnTimer Register

35

Wake-on-SMB 35

Programming Remote Wake-Up Events

35

Power Down 36

Wake-Up

Keep-alive Packets

Installation

37

Activation

39

Transmission Timing

40

Linked Wake-up Pattern to Keep-alive

40

SOS 40

TriggerBits Register

IEEE 802.3x Flow Control 41

IEEE 802.1Q VLANs 42

TCP/IP Checksum Support

System Management Bus (SMBus) Interface

43

Transaction Format 44

Transaction Examples 45

Multiple SMBus Master Arbitration

45

Register Access 46

Transmitting a Packet 46

Receiving a Packet 47

Initiating a Keep-alive Packet

Issuing a Wake-Up Event 47

Monitoring Network Activity

SmbAddress\\

48

SmbArb

49

SmbDiag

SmbFifoData 50

SmbRxBytes

SmbStatus 51

```

### 4 CONFIGURATION

```

Power On Reset 53

System Reset 53

Global Reset 54

Serial EEPROM 54

Flexible EEPROM Format

55

NIC Configuration 55

Forced Configuration 56

Support for Signaling Standards

10 Mbps Signaling

57

100BASE-X Signaling 57

Media-Independent Interface/100BASE-T4

57

Auto-Negotiation 58

BIOS ROM

InternalConfig 58

NIC Initialization

61

Selecting the Media Port

Selection Through EEPROM

Selection Through AutoSelect

MediaOptions 62

AutoSelect Sequence

62

Auto-Negotiation

62

MII/100BASE-T4

62

100BASE-FX 63

Manual Testing of 10BASE-T and 100BASE-TX

Setting the Receive Filter

Station Address

Broadcast Packets 64

Multicast Packets 64

Multicast Address Hash Filter

64

Promiscuous Mode 64

Capabilities Word

MacControl 64

Setting the Duplex Mode 64

PCI Configuration Registers 65

BiosRomControl 65

CacheLineSize 66

CapID

66

CapPtr 66

ClassCode

Data 66

DeviceId 66

HeaderType

InterruptLine 67

InterruptPin

IoBaseAddress 67

LatencyTimer 67

```

MaxLat 68 MemBaseAddress 68 MinGnt 68 NextPtr 68 PciCommand 68 PciStatus RevisionId SubsystemId 70 SubsystemVendorld 70 Vendorld 70

#### 5 EEPROM

Data Format Flexible Format 72 3Com Node Address 72 DeviceId 72 Manufacturing Data 73 Date 73 Division 73 **Product Code** 73 Manufacturerld 73 RomInfo 73 PciParm 73 OEM Node Address Software Information 74 Compatibility Word 75 Capabilities Word 75 InternalConfig 76 Software Information 2 76 Software Information 3 77 Lanworks Data 1 77 SubsystemVendorId 78 SubsystemId 78 MediaOptions 78 Lanworks Data 2 78 SmbAddress PciParm2 78 PciParm3 79 PowerMgmtCtrl PowerConsumption 79 Current IP Address SMBus - OEM Specific 80 Flexible Format 80 Command 80 Data 80 Checksum #2 80 Checksum #3 EepromCommand

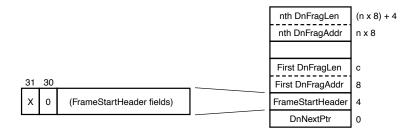

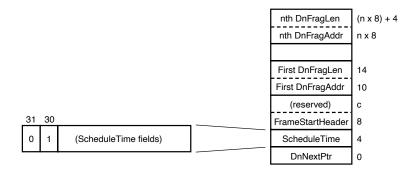

#### 6 DOWNLOAD AND TRANSMISSION

Packet Download Model DPD Data Structure Down Next Pointer 85 Frame Start Header 86 Schedule Time 87 Down Fragment Address 88 Down Fragment Length 88 Packet Download Simple Packet Download 89 Packet Length Round Up 89 Download Scheduling **Download Completion** 90 Multipacket Lists Adding DPDs to the End of the Downlist Inserting a DPD Near the Head of the Downlist 91 Inserting a DPD in Front of a Scheduled DPD Polling on DnNextPtr 92 NIC Download Sequence 92 Original Download Sequence Alternate Download Sequence Packet Transmission 93 **Enabling Transmission** Transmit Errors Underrun Recovery 94 Reclaiming Transmit FIFO Space 94 Transmit Mechanism Limiting dnComplete Interrupts Using CountDown Timer Instead of dnComplete DmaCtrl 95 DnBurstThreshDnListPtr 98 DnMaxBurst 99 DnPoll 100  ${\bf DnPriorityThresh}$ 100 TxFree 101 TxPktId 101 TxReclaimThresh 101 TxStartThresh 102 TxStatus 103

#### 7 RECEPTION AND UPLOAD

Packet Upload Model 104 UPD Data Structure 105 Up Next Pointer 105

Up Pkt Status 105 Up Fragment Address 107 Up Fragment Length 107 Packet Reception 107 Enabling Reception 107 Simple Packet Upload 108 Upload Eligibility 108 Packet Upload Completion 108 Multipacket Lists 108 Early Receive Interrupts 109 Parallel Tasking of Receive Uploads 109 NIC Upload Sequence 109 DmaCtrl 110 MaxPktSize 110 RxEarlyThresh 111 RxFilter 112 RxFree 113 StationAddress 113 StationMask 114 UpBurstThresh 114 UpListPtr 115 UpMaxBurst 115 UpPktStatus 116 UpPoll 117 UpPriorityThresh 118 VlanMask 118

#### 8 INTERRUPTS AND INDICATIONS

IndicationEnable 120

InterruptEnable 120

IntStatus 121

IntStatusAuto 124

#### 9 STATISTICS AND DIAGNOSTICS

BadSSD 126

BytesRcvdOk 126

BytesXmittedOk 127

CarrierLost 127

FramesDeferred 127

FramesRcvdOk 128

FramesXmittedOk 129

LateCollisions 129

MultipleCollisions 130

RxOverruns 130

SingleCollisions 131

SqeErrors 131

UpperBytesOk 132

#### 10 COMMAND REGISTER

Summary of Commands **Unused Command Codes** Reset Commands 136 GlobalReset 136 RxReset 137 TxReset 137 **Transmit Commands** 138 DnStall 138 DnUnstall 138 SetTxReclaimThresh 139 139 SetTxStartThresh TxAgain 139 TxDisable 139 TxDone 139 TxEnable 140 TxFifoBisect 140 Receive Commands 140 RxDisable 140 RxDiscard 141 RxEnable 141 SetHashFilterBit 141 SetRxEarlyThresh 141 SetRxFilter 142 UpStall 142 UpUnStall 142 Interrupt Commands 143 AcknowledgeInterrupt RequestInterrupt SetIndicationEnable 143 SetInterruptEnable 144 Other Commands 144 DisableDcConverter 144 EnableDcConverter 144 SelectRegisterWindow 144 StatisticsDisable 146 StatisticsEnable 146

#### 11 AUTO-NEGOTIATION AND MII REGISTERS

Overview 147

40-0574-xxx or 40-05772-xxx ASIC Auto-Negotiation Registers 147

Autonegotiation Advertisement 148

Autonegotiation Expansion 148

Autonegotiation Link Partner Ability 149

Control 149

Device Specific 1 150 Device Specific 2 151 Device Specific 3 152 Next Page Transmit 153 PHY Identification 1 153 PHY Identification 2 154 Quick Status 154 Status 155 40-0579-xxx ASIC Auto-Negotiation Registers 10BASE-T Auxiliary Error and General Status 157 100BASE-X Auxiliary Control 159 100BASE-X Auxiliary Status 160 100BASE-X Disconnect Counter 100BASE-X False Carrier Sense Counter 161 100BASE-X Receive Error Counter Auto-Negotiation Advertise Auto-Negotiation Expansion 163 Auxiliary Control/Status 164 Auxiliary Mode 165 Auxiliary Multiple PHY Auxiliary Status Summary Control 169 Interrupt 171 Link Partner Ability 171 PHYID High 172 PHYID Low 172 Status 173

#### 12 OTHER REGISTERS

BiosRomAddr 175 BiosRomData 176 ConfigAddress 176 ConfigData 177 DebugControl 177 DebugData 177 FifoDiagnostic 178 Media 179 MacControl 179 MediaOptions 181 MediaStatus 182 NetworkDiagnostic 184 Physical Mgmt 186 PowerMgmtCtrl 187 ResetOptions 187 SosBits 189 **Timers and Counters** 189 Countdown 189 FreeTimer 190

RealTimeCnt 190 Timer 192 VlanEtherType 192

#### A AUTOSELECT PSEUDO CODE

AutoSelect Sequence 193

### B PROGRAMMING THE MII MANAGEMENT INTERFACE

Management Frame Formats 196

Read Frame 196

Write Frame 197

Read Cycle 197

Write Cycle 197

Z Cycle 197

#### **C** FRAME FORMATS

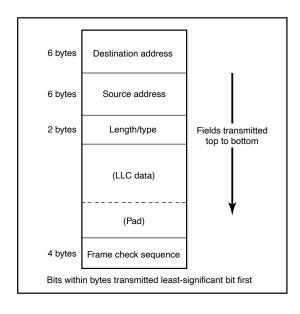

IEEE 802.3 MAC Frame Format 198

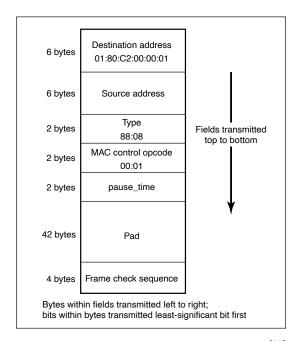

IEEE 802.3x PAUSE Frame Format 199

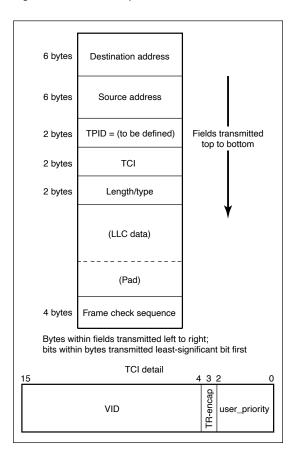

IEEE 802.1q Frame Format 200

#### D ERRATA LIST AND SOLUTIONS

INDEX

**INDEX OF REGISTERS**

**INDEX OF BITS**

## **FIGURES**

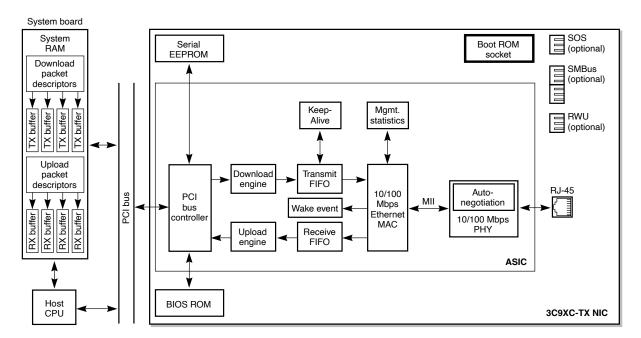

- 1 3C90xC System Architecture 18

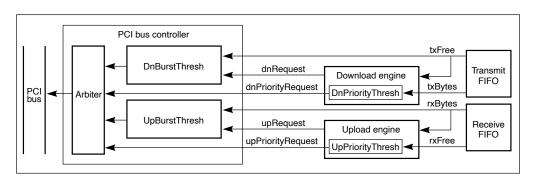

- 2 3C90xC NIC Bus Request Structure 26

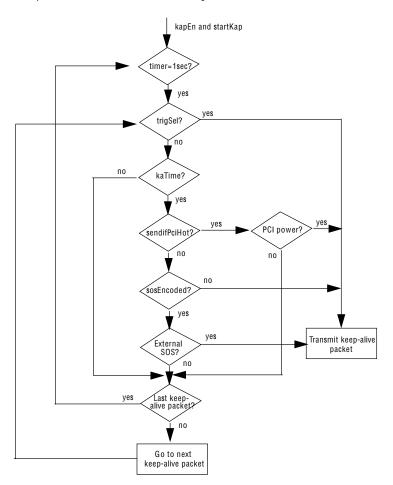

- 3 Keep-alive Packet Transmission Timing 40

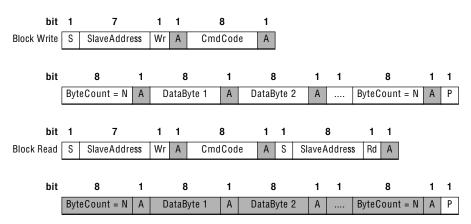

- 4 SMBus Master Arbitration Flow 46

- 5 Internal Reset Structure 54

- 6 Downlist 84

- 7 Type 0 DPD Format 85

- 8 Type 1 DPD Format 85

- **9** Uplist 104

- **10** UPD Format 105

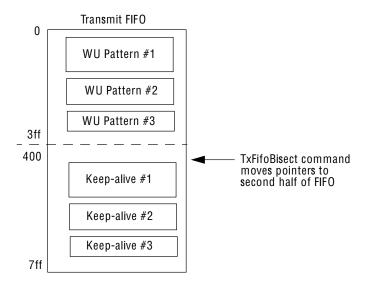

- 11 TxFifoBisect Command 140

- 12 IEEE 802.3 MAC Frame Format 198

- 13 IEEE 802.3x PAUSE Frame Format 199

- **14** IEEE 802.1q Frame Format 200

# **TABLES**

22 3C90xC NIC Anomalies 201

| 1  | 3C90xC NICs 14                                                         |     |

|----|------------------------------------------------------------------------|-----|

| 2  | 3C90xC NIC ASICs 18                                                    |     |

| 3  | 3C90xC Host Register Layout 23                                         |     |

| 4  | 3C90xC Register Window Layout 24                                       |     |

| 5  | 3C90xC NIC PCI Memory Commands 25                                      |     |

| 6  | 3C90xC NIC Power States 28                                             |     |

| 7  | SOS Pins 41                                                            |     |

| 8  | EEPROM Data Locations 54                                               |     |

| 9  | PCI Registers Set During Configuration 56                              |     |

| 10 | Summary of PCI Configuration Registers 65                              |     |

| 11 | EEPROM Contents 71                                                     |     |

| 12 | Flexible EEPROM Format 72                                              |     |

| 13 | 3C90xC NICs Summary of Capabilities 75                                 |     |

| 14 | Interrupt-specific Actions 119                                         |     |

| 15 | Summary of Transmit Statistics 125                                     |     |

| 16 | Summary of Receive Statistics 126                                      |     |

| 17 | Command Summary 135                                                    |     |

| 18 | Summary of 40-0574-xxx or 40-05772-xxx ASIC Auto-Negotiation Registers | 147 |

| 19 | Summary of 40-0579-xxx ASIC Auto-Negotiation and MII Registers 157     |     |

| 20 | Loopback Modes 186                                                     |     |

| 21 | Management Frame Formats 196                                           |     |

## Introduction

This technical reference describes the basic architecture and defines the programming interface of the 3Com® EtherLink® and EtherLink Server 10/100 PCI network interface cards (NICs). The NIC models are listed in Table 1.

Table 1 3C90xC NICs

| Model       | Description                                         | Notes                        |

|-------------|-----------------------------------------------------|------------------------------|

| 3C905C-TX   | EtherLink 10/100 PCI NIC for Complete PC Management | Includes boot ROM socket     |

| 3C905C-TX-M | EtherLink 10/100 PCI NIC for Complete PC Management | Includes MBA boot flash ROM. |

| 3C980C-TXM  | EtherLink Server 10/100 PCI NIC                     | Includes MBA boot flash ROM. |

Specifications in this technical reference apply to all listed NICs unless the text designates a specific model.

#### 3C90xC NIC Features

The 3C90xC NIC contains the following features:

- 2 KB transmit FIFO and 2 KB receive FIFO.

- True dual-channel DMA engine.

- Enhanced scatter-gather engines reduce the number of I/O operations required to support data transfers (compared to the 3C905B NIC).

- A download-scheduling mechanism that allows a packet to be downloaded at some specific future time. For example, download scheduling can be used to support video or audio streams over a LAN, or to avoid overflowing a switch's buffers when the switch is communicating with a lower-speed device.

- A hash filter that provides improved multicast packet handling (compared to the 3C905B NIC).

- Support for VLANs and IEEE 802.3x flow control functions.

- Support for IEEE 802.3u auto-negotiation (10BASE-T and 100BASE-TX).

- Support for ACPI Power Management.

- Support for wake-up events

- Improved bus master efficiency through use of optimal PCI memory commands and support of larger burst lengths.

- Multipacket, multifragment scatter operations for uploads

- Multipacket, multifragment gather operations for downloads

- Simultaneous upload and download operations

- On-chip RAM that can be used instead of external RAM

- TCP/IP checksum features.

- Direct register access to BIOS ROM.

- An integrated 100 Mbps PHY that eliminates the need for an external 100 Mbps transceiver.

- Two-wire SMBus (System Management Bus) that provides register, configuration, and transmit and receive FIFO access.

- Flexible EEPROM loads; any internal register can be written, commands can be issued, and transmit FIFO can be loaded.

- Keep-alive packets that can be stored in the transmit FIFO and sent out at specific time intervals during sleep mode. These packets can also be "linked" to a specific pattern match effectively performing an "ack" function.

- SOS hardware pins that are linked to one of the keep-alive packets. These are intended for alerting the management console that some abnormal event (such as a case intrusion) has occurred.

- PCI 2.2 compliance, which includes proper handling of PCIReset, sensing 3.3V-AUX, a very low power mode (less than 20 mA), and reporting total current consumption.

# About This Technical Reference

This technical reference contains programming interface information that software engineers, independent software developers, and test engineers require to write device drivers, diagnostic programs, and production test software for 3C90xC NICs.

This information includes:

- Theory of operation; for example, how transmission and reception occur.

- Register set, including the size, type, address, and function of each register and the functions of the bits in the register.

The information in this reference is language-independent. It applies regardless of the programming language you use to write the driver or other software program.

In this reference, addresses refer to physical addresses, not to logical or virtual addresses. Numeric values other than **Decimal** values are presented in the following formats:

| Format  | Description                                          | Example                                |

|---------|------------------------------------------------------|----------------------------------------|

| #'rZZZZ | # is the number of bits.                             | 6'b100101 is a 6-bit binary notation.  |

|         | ' is a delimiter.                                    | 6'h25 is a 6-bit hexadecimal notation. |

|         | r is the radix (b for binary and h for hexadecimal). |                                        |

|         | ZZZZ is the value.                                   |                                        |

| ZZZr    | ZZZ is the value.                                    | 100101b is a binary notation.          |

|         | r is the radix (b for binary and h for hexadecimal). | 25h is a hexadecimal notation.         |

**Terms and Acronyms**

The following terms and acronyms are used in this reference:

| Term or Acronym     | Meaning                                                                                                    |

|---------------------|------------------------------------------------------------------------------------------------------------|

| ACK                 | Acknowledge.                                                                                               |

| BIST                | Built-in self test.                                                                                        |

| Byte                | An 8-bit wide quantity of data.                                                                            |

| Double word (dword) | A 32-bit wide quantity of data (4 bytes).                                                                  |

| Download            | The process of transferring transmit data from system memory to $\ensuremath{NIC}.$                        |

| DPD                 | Download packet descriptor.                                                                                |

| FIFO                | First in, first out.                                                                                       |

| FLP                 | Fast link pulse.                                                                                           |

| FSH                 | Frame start header.                                                                                        |

| Indication          | The reporting of any interesting event on the NIC. Any indication may be configured to cause an interrupt. |

| Interrupt           | The actual assertion of the host machine's interrupt signal.                                               |

| ISR                 | Interrupt Service Routine                                                                                  |

| MII                 | Media-Independent Interface.                                                                               |

| NIC                 | Network interface card.                                                                                    |

| NOS                 | Network operating system.                                                                                  |

| PEROM               | Programmable and erasable read-only memory.                                                                |

| PHY                 | IEEE designation for Physical layer.                                                                       |

| Remote Wake-Up      | The ability to power on a networked PC that is in standby or suspend mode using a wake-up event.           |

| SMBus               | System Management Bus                                                                                      |

| UDP                 | User datagram protocol.                                                                                    |

| UPD                 | Upload packet descriptor.                                                                                  |

| Upload              | The process of transferring receive data from NIC to system memory.                                        |

| WOL                 | Wake on LAN (also known as Remote Wake-Up).                                                                |

| Word                | A 16-bit wide quantity of data (2 bytes).                                                                  |

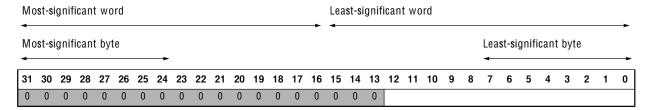

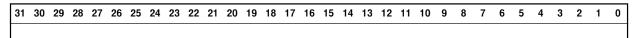

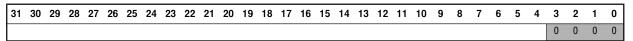

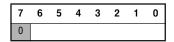

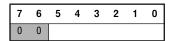

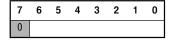

## **Register Bit Maps** The register descriptions in this technical reference include register bit maps. For example:

The first row of a bit map shows the bit numbers.

The second row of the bit map indicates the following information:

- Shaded areas indicate one of the following:

- Read-only bits. These bits read back the default values shown. If no value is shown, the read-back value varies.

- Unimplemented, reserved bits. These bits may be placeholders for possible use in a future revision of the NIC, or they may provide diagnostic information. Reserved bits are writable, but they do not control any function. They disregard data written to them and return zeros when they are read. To maintain compatibility with future versions of the NIC, drivers should write zeroes to reserved bits.

- Unshaded areas indicate active bits. The functions of these bits are described in the register descriptions. A value in an unshaded bit indicates that the driver must write that value to the bit.

- Vertical lines mark the boundaries of fields of bits (for example, [12:0]).

Default bit values are indicated as follows:

- 0 and 1 are known default states.

- x is a bit that is not initialized at reset; thus, its value varies.

# 2

## **ARCHITECTURE**

This chapter describes the 3C90xC NIC system architectures and ASIC block diagrams. It also summarizes the layout of the host registers and windows.

#### 3C90xC NIC Block Diagram

The block diagram for the 3C90xC NICs is shown in Figure 1. The NIC devices are described at the end of this chapter.

Figure 1 3C90xC System Architecture

#### **ASICs**

Table 2 describes the 3C90xC ASIC versions.

Table 2 3C90xC NIC ASICs

| ASIC Number  | Description                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------|

| 40-0579-xxx  | 3.3-volt ASIC with an internal voltage regulator that allows it to operate in a 5-volt environment. |

| 40-0574-xxx  | 3.3-volt ASIC with an internal voltage regulator that allows it to operate in a 5-volt environment. |

| 40-05772-xxx | 5-volt                                                                                              |

Specifications in this technical reference apply to all ASIC versions unless the text designates a specific ASIC number.

Hardware Identification

To physically identify which ASIC is on a 3C90xC NIC, look at the ASIC number inscribed on the ASIC. (See Table 2 for a list of ASIC numbers.)

Software Identification

To identify through software which ASIC is on a 3C90xC NIC, view the chip/Vendor bit in the RevisionId register. See "RevisionId" in Chapter 4.

**ASIC Block Descriptions**

The devices associated with the ASICs are described below. For more information, see Figure 1.

#### **PCI Bus Controller**

This block implements the PCI interface functions (responding to PCI target cycles, generating and controlling PCI master cycles, and performing parity checking and generation).

The PCI bus controller logic also provides bus master services to the download and upload engines and provides the logic to control the BIOS ROM and serial EEPROM devices.

#### **Upload and Download Engines**

These blocks fetch the descriptors in the uplist and downlist and perform bus master data transfers by requesting PCI bus master burst service from the PCI bus controller block.

The upload engine removes receive data from the receive FIFO and supplies it to the PCI bus as it is required.

The download engine pipes transmit data from the PCI bus into the transmit FIFO.

#### **Transmit and Receive FIFOs**

These blocks are high-speed burst caches. These blocks each contain 2 KB of data buffering and the logic required to manage the FIFOs.

The transmit FIFO, in addition to performing normal transmit operations, is also used to store both Wake-On-LAN patterns and keep-alive packets while in sleep mode. See Chapter 3 for specific operation.

#### 10/100 Mbps Ethernet MAC

This block implements the IEEE 802.3 Media Access Control (MAC) function. It is responsible for the media access protocol, including deference, collision recovery and back off, receive packet filtering, and error detection. This block also provides information to the management statistics function.

#### **Management Statistics**

This block accumulates various network events statistics in hardware. Driver software reads these statistics periodically to maintain a network management information base (MIB).

#### **Auto-Negotiation**

This block provides the IEEE 802.3u auto-negotiation function.

Auto-negotiation provides a means for the two devices in a link segment to communicate their signaling capabilities and automatically select the best mode. Auto-negotiation only manages twisted-pair-based signaling.

#### 10/100 Mbps PHY

This block replaces the 10BASE-T/AUI, 100 Mbps signaling, and auto-negotiation functions found in 3C90x and 3C90xB NICs. It integrates the following functions:

- IEEE 802.3 Media Access Control (MAC) function. The protocol, includes deference, collision recovery and back off, receive packet filtering, and error detection. This block provides information to the management statistics function.

- Auto-negotiation provides a means for the two devices in a link segment to communicate their signaling capabilities and automatically select the best mode. Auto-negotiation only manages twisted-pair-based signaling, so on the 3C90xB NICs, it covers only the 10BASE-T and 100BASE-TX ports. On 3C900B NICs, it covers 10BASE-T signaling.

- 10BASE-T/AUI interface supports 10BASE-T, AUI, and thin coax (10BASE2) media types. Only filtering magnetics are required off-chip to implement a complete 10BASE-T solution.

#### **Keep-Alive**

Keep-alive packets allow a NIC that is in sleep mode (i.e., the PCI host is powered down) to transmit packets to refresh its presence in various network routing tables.

#### **Wake Event**

The NIC will generate a wakeup signal as a result of any of three standard wakeup events: Wakeup Packet reception, Magic Package reception, or change in link state.

#### **SOS Connector**

The SOS connector allows a system configuration where an external event (e.g., fan speed, over-temperature, over-voltage) causes a transmission of an alert packet over the network.

#### **SMBus Connector**

Attaching an SMBus controller to this connector allows:

- Arbitration with multiple SMBus master controllers

- Access to any ASIC register, including I/O and Configuration registers

- Issuing of commands (via the Command register)

- EEPROM read and write

- Reception Send and Receive packets

- Issuing of a System Wakeup (with assertRemotePme)

- Monitoring of network activity (through txActivity and rxActivity)

#### **RWU Connector**

The Remote Wake Up connector can be used to support WOL applications. Upon receiving a wakeup packet, a PME signal is generated, waking up the host system.

#### Other NIC Devices

The other devices associated with NIC operation are described below.

#### **BIOS ROM**

The optional BIOS ROM can contain up to 128 KB of code that is executed at system boot time.

NICs generally come with a BIOS ROM socket that allows field installation and upgrade of the boot code.

The following boot roms are supported:

- AT29C512

- AT49F010

- AT49BV512

- AT49F001N

- AT49LV001NT

- AT29LV512

- AT29LV010B

- SST29EE010

- SST29LE010

- SST39SF010

- SST39VF010

- SST39VF512

- STM29W512B

- AM29LV010B

#### **Serial EEPROM**

The 16-bit  $\times$  256-word and 16-bit  $\times$  1024-word serial EEPROM devices store configuration information for the NIC, including PCI device ID, station address, and transceiver selection. The type of EEPROM device installed is determined by a "power-on reset" register stuffing option. See the ResetOptions register for more information.

#### **Host Registers**

This section shows the host register layouts for the 3C90xC NIC.

The NIC interacts with the host CPU through registers. The registers are mapped into 128 bytes of the host CPU's I/O space, memory space, or both. (Although registers are sometimes called "I/O registers," they may in fact be mapped and accessed in memory space.)

The first 16 bytes in the register space are a switchable window into one of eight register banks. A driver issues the SelectRegisterWindow command to the NIC to select which bank is visible in the window. The remaining 112 bytes in the register space are a flat address decode.

A register's location is specified by its offset from a base address that is defined in the loBaseAddress PCI register, or, in the case of registers residing within a window, its window number and its offset within the window. For example, the address to be used for I/O access of the BIOS ROM is held in the BiosRomAddr register in window 0, offset 7.

#### Bit Widths of Register Accesses

In general, registers must be accessed as operands that are no wider than the bit width of the register. For example, although the BytesRcvdOk, UpperFramesOk, and FramesDeferred registers all appear in the double word at offset 8 in window 6, it is not legal to read all three registers with a single 32-bit I/O read instruction. Additionally, because of internal architecture limitations, the StationAddress register must be accessed with no larger than word-wide cycles.

Some registers cannot be accessed with cycles narrower than the register. Specific register access limitations are described in the register definitions in this technical reference.

#### **Command Register**

Many of a driver's interactions with the NIC are performed using a command structure. Commands are codes, which sometimes include a parameter, that are written to the NIC to perform some action. For example, the RxEnable command causes the NIC transceiver to start accepting receive packets from the network.

Commands are written to the write-only Command register, which appears at offset e in every window. For details on the commands, see Chapter 10, "Command Register."

#### **Interrupt Status Register**

The read-only IntStatus register shares the location offset e with the write-only Command register. A driver uses IntStatus to determine the sources of interrupts on the NIC and to determine which window is currently visible. IntStatus also includes a bit that indicates when a command issued to the Command register is in the process of being executed.

The 3C90xC NICs have a special version of the IntStatus register, the IntStatusAuto register. Reading IntStatusAuto returns the value in IntStatus and causes some side effects that help optimize interrupt service routines.

# 3C90xC NIC Register Layout

The host register layouts and register window layouts for the 3C90xC NIC are shown in Table 3 and Table 4.

Shaded areas indicate reserved spaces that are not implemented. Do not program in these spaces.

Table 3 3C90xC Host Register Layout

| Byte 3   | Byte 2        | Byte 1          | Byte 0           | Offset |  |  |  |

|----------|---------------|-----------------|------------------|--------|--|--|--|

|          | PowerMgmtCtrl |                 |                  |        |  |  |  |

| Up       | MaxBurst      | DnMa            | DnMaxBurst       |        |  |  |  |

|          |               | Debug           | Control          | 74     |  |  |  |

|          | Deb           | ugData          |                  | 70     |  |  |  |

|          |               |                 |                  | 6c     |  |  |  |

|          |               |                 |                  | 68     |  |  |  |

|          |               |                 |                  | 64     |  |  |  |

|          |               |                 |                  | 60     |  |  |  |

|          |               |                 |                  | 5c     |  |  |  |

|          |               |                 |                  | 58     |  |  |  |

|          |               |                 |                  | 54     |  |  |  |

|          |               |                 |                  | 50     |  |  |  |

|          |               |                 |                  | 4c     |  |  |  |

|          |               |                 | ConfigData       | 48     |  |  |  |

|          |               |                 | ConfigAddress    | 44     |  |  |  |

|          | Real          | Time Cnt        |                  | 40     |  |  |  |

|          | UpBurstThresh | UpPoll          | UpPriorityThresh | 3c     |  |  |  |

|          | Up            | ListPtr         | 1                | 38     |  |  |  |

| Co       | ountdown      | Free            | Timer            | 34     |  |  |  |

|          | UpP           | ktStatus        |                  | 30     |  |  |  |

|          |               | DnPoll          | DnPriorityThresh | 2c     |  |  |  |

|          | DnBurstThresh |                 |                  | 28     |  |  |  |

|          |               | ListPtr         |                  | 24     |  |  |  |

|          |               | naCtrl          |                  | 20     |  |  |  |

|          | StatusAuto    |                 |                  | 1c     |  |  |  |

| TxStatus | Timer         |                 | TxPktId          | 18     |  |  |  |

|          |               |                 |                  | 14     |  |  |  |

|          |               |                 |                  | 10     |  |  |  |

|          | Register Wind | ows 0 through 7 |                  | С      |  |  |  |

|          | (See          | Table 4)        |                  | 8      |  |  |  |

|          |               |                 |                  | 4      |  |  |  |

|          |               |                 |                  | 0      |  |  |  |

Table 4 3C90xC Register Window Layout

| Byte 3 Byte 2    |                    | Byte 1              | Byte 0         | Offset | Window |

|------------------|--------------------|---------------------|----------------|--------|--------|

| IntStatus /      | Command            | PowerMo             | gmtEvent       | С      | 7      |

|                  |                    |                     |                | 8      |        |

|                  |                    | VlanEth             |                | 4      |        |

|                  |                    | Vlanl               | Mask           | 0      |        |

|                  |                    |                     |                |        |        |

|                  | Command            | BytesXm             |                | С      | 6      |

|                  | RcvdOk             | UpperFramesOk       | FramesDeferred | 8      |        |

| FramesRcvdOk     | FramesXmittedOk    | RxOverruns          | LateCollisions | 4      |        |

| SingleCollisions | MultipleCollisions | SqeErrors           | CarrierLost    | 0      |        |

|                  |                    |                     |                |        |        |

|                  | Command            | Indicatio           |                | С      | 5      |

|                  | otEnable           | TxReclaimThresh     | RxFilter       | 8      |        |

| RxEarly          | /Thresh            |                     |                | 4      |        |

|                  |                    | TxStart             | Thresh         | 0      |        |

|                  |                    |                     | D 100D         |        |        |

|                  | Command            | UpperBytesOk        | BadSSD         | C      | 4      |

|                  | Status             | Physica             | 8              | -      |        |

|                  | Diagnostic         | FifoDia             | 4              |        |        |

| VcoDiagnostic    | (not supported)    |                     |                | 0      |        |

| IntStatue        | Command            | TxF                 | raa            | С      | 3      |

|                  | Free               | Media               | 8              | -      |        |

|                  | ontrol             | MaxP                | 4              |        |        |

| Widoo            |                    | alConfig            | K(0)20         | 0      | -      |

|                  |                    |                     |                |        |        |

| IntStatus /      | Command            | ResetO              | ptions         | С      | 2      |

| Station          | Mask (Hi)          | StationM            | 8              | -      |        |

|                  | Mask (Lo)          | StationAd           | 4              | -      |        |

| StationAd        | dress (Mid)        | StationAd           | 0              | -      |        |

|                  |                    | I.                  |                |        |        |

| IntStatus /      | Command            | Trigg               | erBits         | С      | 1      |

|                  | SosBits            | WakeO               | nTimer         | 8      | -      |

| SmbR             | SmbRxBytes         |                     | SmbArb         | 4      |        |

| Smbs             | Status             | Smb Addre <b>ss</b> | SmbFifoData    | 0      |        |

|                  |                    | •                   |                | 1      |        |

|                  | Command            | Eeproi              |                | С      | 0      |

| EepromC          | Command            |                     | BiosRomData    | 8      |        |

|                  | BiosRo             | mAddr               |                | 4      |        |

|                  |                    |                     |                | 0      |        |

# 3

## **OPERATION**

This chapter summarizes NIC operational characteristics.

#### **Data Structure Lists**

To move data between the host and the NIC, drivers set up data structures in system RAM to specify the buffers to be used for packet data movement. These data structures, called descriptors, are linked together in system memory to form lists.

All packet data is moved across the NIC PCI bus by bus master operations. The NIC also uses bus master operations to read descriptor information out of system RAM and to write status back into the descriptors.

Movement of a transmit packet to the NIC is called a download. The list of download packet descriptors (DPDs) is called the *downlist*. Similarly, a receive packet movement is called an upload, and the list of upload packet descriptors (UPDs) is the *uplist*.

The device driver creates and maintains the uplist and the downlist. It starts the download process by writing the address of the first download descriptor in the downlist to the DnListPtr register. Uploads are started by writing the first upload descriptor address to the UpListPtr register. The device driver also accesses NIC registers for initialization, interrupt handling, statistics collection, and error handling.

For details on data structure lists, see Chapter 6 and Chapter 7.

# PCI Bus Master Operation

This section describes aspects of bus master operation that can be controlled by software. For information about PCI configuration, see "PCI Configuration Registers" in Chapter 4.

#### **PCI Memory Commands**

The 3C90xC NIC supports the PCI memory commands summarized in Table 5. The NIC decides on a burst-by-burst basis which command to use.

Table 5 3C90xC NIC PCI Memory Commands

| Command | Description             |

|---------|-------------------------|

| MW      | Memory Write            |

| MWI     | Memory Write Invalidate |

| MR      | Memory Read             |

| MRL     | Memory Read Line        |

| MRM     | Memory Read Multiple    |

|         |                         |

MR is used for all fetches of descriptor information. For reads of transmit packet data, MR, MRL, or MRM is used, depending upon the remaining number of bytes in the fragment, the amount of free space in the transmit FIFO, and whether the upload engine is requesting a bus master operation.

MW is used for all descriptor writes. Writes of receive packet data use either MW or MWI, depending upon the remaining number of bytes in the fragment, the amount of packet data in the receive FIFO, and whether the download engine is requesting a bus master operation.

Three configuration bits control the use of advanced PCI memory commands:

- The MWIEnable bit in the PciCommand configuration register allows the system to enable or disable the NIC's use of MWI.

- The defeatMWI bit in the DmaCtrl register allows the driver to disable the NIC's use of MWI. By default, MWI is enabled.

- The defeatMRL bit in the DmaCtrl register allows the driver disable the NIC's use of MRL. By default, MRL is enabled.

#### **PCI Bus Request Control**

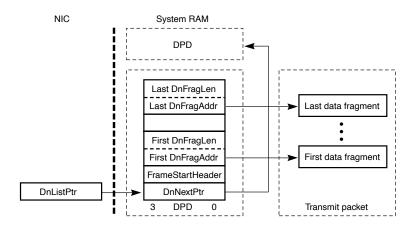

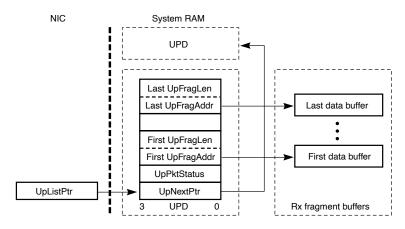

The NIC provides a set of registers that control PCI burst behavior. These registers allow trade-offs to be made between PCI bus efficiency and underrun/overrun frequency. Figure 2 illustrates the bus request structure.

Figure 2 3C90xC NIC Bus Request Structure

Arbitration logic (the arbiter) within the PCI bus controller block accepts bus requests from the download and upload engines.

#### Download

The download engine monitors the amount of free space in the transmit FIFO. When there are at least 16 bytes of free space and a fragment available for download, the download engine uses the dnRequest bit to make a standard bus request. The DnBurstThresh logic register qualifies dnRequest. When the amount of free space in the FIFO is greater than the value in the DnBurstThresh register, a download request is passed on to the arbiter. The purpose of DnBurstThresh is to delay the bus request until there is enough free space in the FIFO for a long, efficient burst.

The download engine also has a way to make an emergency bus request. When the number of used bytes in the FIFO drops below the value in the DnPriorityThresh register, indicating that the FIFO is approaching an underrun condition, the dnPriorityRequest bit makes a priority request. This request is not subject to the DnBurstThresh constraint; when the FIFO is close to underrun, burst efficiency is sacrificed in favor of requesting the bus as quickly as possible.

#### Upload

The upload mechanism is similar to download. The upload engine monitors the number of bytes in the receive FIFO. When there are enough bytes to make the packet visible and a buffer is available for upload, the upload engine uses the upRequest bit to make a standard bus request. The UpBurstThresh logic register qualifies the upRequest bit. When the number of bytes in the FIFO is greater than the value in the UpBurstThresh register, an upload request is passed on to the arbiter. Priority requests prevent receive overruns. The upPriorityRequest bit is asserted when the free space in the receive FIFO falls below the value in the UpPriorityThresh register.

The arbiter services the four requests in this fixed priority order:

- 1 upPriorityRequest

- 2 dnPriorityRequest

- 3 upRequest/dnRequest (upload and download alternate if both requests are present)

#### **Power Management**

The NIC supports power management directed by the operating system, in accordance with the *Advanced Configuration and Power Management (ACPI)*Specification. The following paragraphs describe the power management features.

#### **Power Up Sequencing**

The PCI 2.2 Bus Specification dictates power restrictions for NICs that use the auxiliary 3.3-volt power supply. Specifically, the specification states that a NIC shall not use more than 20 mA while in the D3cold state if the NIC is not enabled to source the PME# system wake-up signal. (For more information on the D3 cold state, see Table 6.

Through a special power-up sequencing, the NIC determines whether it can operate in a normal mode or whether it must power up in a 20 mA mode (only auxiliary power present) by reading a control word from the EEPROM. If the NIC powers up in a 20 mA mode, it does not respond to incoming packets or SMBus activity. To recover from this mode, the PCI main power must be restored.

#### Low-power Mode

The 3C90xC NIC supports D3cold, a very low-power mode. If the NIC is receiving auxiliary current and it is not enabled as a wake-up device, the NIC goes into a 20 mA mode. In this mode, the NIC is essentially "dead" and does not respond to any cycles (through the PCI bus, network, or SMBus). To restore normal operation, assert PCI main power back to the PCI bus.

#### **Power States**

Table 6 defines the supported power states. The current power state is determined by the powerState field in the PowerMgmtCtrl register.

Table 6 3C90xC NIC Power States

| State                       | powerState Value | Description                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0 <sub>uninitialized</sub> | 0                | This state is a result of a hardware reset, or of a transition from D3 $_{\rm hot}$ to D0. This state is the same as D0 $_{\rm active}$ except that the PCI configuration registers are uninitialized. In this state, the NIC responds to PCI configuration cycles or SMBus cycles.                                                         |  |  |  |  |  |

| D0 <sub>active</sub>        | 0                | This is the normal operational power state for the NIC.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                             |                  | In this state, the PCI configuration registers have been initialized by the system, including the ioSpace, memorySpace, and busMaster bits in the PciCommand register, so the NIC is able to respond to PCI I/O, memory and configuration cycles, and can operate as a PCI master.                                                          |  |  |  |  |  |

|                             |                  | The 3C90xC NIC supports both wake-up events and SMBus cycles in this state.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| D1                          | 1                | This is a "light-sleep" state, which allows transition back to D0 with no delay.<br>Support for D1 is determined by the d1Support bit in the PciParm2 word in<br>EEPROM.                                                                                                                                                                    |  |  |  |  |  |

|                             |                  | In this state, the NIC responds to PCI configuration accesses, allowing the system to change the power state, but it does not respond to any PCI I/O or memory accesses.                                                                                                                                                                    |  |  |  |  |  |

|                             |                  | The NIC's function in the D1 state is to recognize wake-up events and pass them on to the system by asserting the PME# signal on the PCI bus.                                                                                                                                                                                               |  |  |  |  |  |

|                             |                  | The 3C90xC NIC also responds to SMBus cycles in this state.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| D2                          | 2                | This is a partial power-down state that allows a faster transition back to D0 than is possible from the D3 state. Support for D2 is determined by the d2Support bit in the PciParm2 word in EEPROM.                                                                                                                                         |  |  |  |  |  |

|                             |                  | Like the D1 state, the NIC in the D2 state responds to PCI configuration accesses, allowing the system to change the power state, but it does not respond to any PCI I/O or memory accesses.                                                                                                                                                |  |  |  |  |  |

|                             |                  | Similarly, the function of the NIC in the D2 state is to recognize wake-up events and pass them on to the system by asserting the PME# signal on the PCI bus.                                                                                                                                                                               |  |  |  |  |  |

|                             |                  | The 3C90xC NIC also responds to SMBus cycles in this state.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| D3 <sub>hot</sub>           | 3                | This is the full power-down state for the NIC. In D3 $_{\rm hot}$ , the NIC loses all PCI configuration information except for the value in the powerState bit.                                                                                                                                                                             |  |  |  |  |  |

|                             |                  | In this state, the NIC responds to PCI configuration accesses, to allow the system to change the power state back to ${\rm D0_{uninitialized}}$ , but it does not respond to any PCI I/O or memory accesses.                                                                                                                                |  |  |  |  |  |

|                             |                  | The NIC's function in the $\rm D3_{hot}$ state is to recognize wake-up events and pass them on to the system by asserting the PME# signal on the PCI bus.                                                                                                                                                                                   |  |  |  |  |  |

|                             |                  | The 3C90xC NIC also responds to SMBus cycles in this state.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| D3 <sub>cold</sub>          | N/A              | This is the power-off state for the NIC from a bus point of view. The NIC has no function in this state unless auxiliary current is supplied. If auxiliary power is supplied, the NIC's function in the D3 <sub>cold</sub> state is to recognize wake-up events and pass them on to the system by asserting the PME# signal on the PCI bus. |  |  |  |  |  |

|                             |                  | The 3C90xC NIC also responds to SMBus cycles in this state.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                             |                  | When power is restored, the system guarantees the assertion of hardware reset, which puts the NIC into the $D0_{uninitialized}$ state.                                                                                                                                                                                                      |  |  |  |  |  |

#### **Power Management** Registers

Power management registers are in the PCI configuration space, as defined by the PCI Bus Power Management Interface Specification, Revision 1.0.

#### **PowerMgmtCap**

Provides information about the NIC's power management capabilities. Synopsis

Read-only Type 16 bits Size Offset from CapPtr

The PowerMgmtCap register supplies the system with information about the NIC's power management support and capabilities. The PowerMgmtCtrl register allows system or driver software to read the NIC's power management status and set the NIC's power state.

The reset default is 7601h, but several bits are loaded from EEPROM shortly after reset.

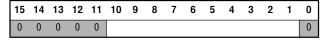

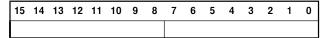

#### PowerMgmtCap Register Format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |

#### PowerMgmtCap Bit Descriptions

| Bit     | Name       | Description                                                                                                                        |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| [2:0]   | version    | This read-only field returns the PCI Bus Power<br>Management Specification adherence value:                                        |

|         |            | <ul> <li>001 = Adheres to PCI Bus Power Management<br/>Specification version 1.0.</li> </ul>                                       |

|         |            | <ul> <li>010 = Adheres to PCI Bus Power Management<br/>Specification version 1.1.</li> </ul>                                       |

| [9]     | d1Support  | This read-only bit, when set, indicates that this device supports the D1 power state.                                              |

|         |            | The value of this bit is determined by bit 4 (d1Support) in the EEPROM PciParm word.                                               |

| [10]    | d2Support  | This read-only bit, when set, indicates that this device supports the D2 power state.                                              |

|         |            | The value of this bit is determined by bit 5 (d2Support) in the EEPROM PciParm word.                                               |

| [15:11] | pmeSupport | This read-only field indicates the power states from which this device is able to generate a power management event (assert PME#). |

|         |            | Each bit corresponds to a power state. A zero in a particular bit indicates that events cannot be generated from that state.       |

|         |            | The bits are defined as follows:                                                                                                   |

|         |            | <ul> <li>xxxx1: Power management events possible from D0.</li> </ul>                                                               |

|         |            | <ul> <li>xxx1x: Power management events possible from D1.</li> </ul>                                                               |

|         |            | <ul> <li>xx1xx: Power management events possible from D2.</li> </ul>                                                               |

|         |            | $\blacksquare$ x1xxx: Power management events possible from D3 $_{hot}.$                                                           |

#### PowerMgmtCap Bit Descriptions (continued)

| Bit     | Name                        | Description                                                                         |

|---------|-----------------------------|-------------------------------------------------------------------------------------|

|         |                             | <ul> <li>1xxxx: Power management events possible from D3<sub>cold</sub>.</li> </ul> |

|         | C90xC NIC suppo<br>m2 word. | orts wake-up events from all D-states. Bits [15:11] are loaded from the EEPROM      |

| (2 of 2 | 2)                          |                                                                                     |

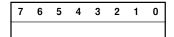

#### **PowerMgmtCtrl**

Allows control over the power state and the power management interrupts. Synopsis

Read/write Type Size 16 bits Offset from CapPtr

The reset default is 0000h.

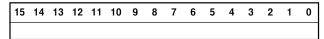

#### PowerMgmtCtrl Register Format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   |   | 0 | 0 | 0 | 0 | 0 | 0 |   |   |

#### PowerMgmtCtrl Bit Descriptions

| Bit    | Name                | Description                                                                                                                                                                                    |

|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1:0]  | powerState          | This read/write field is used to determine or set the NIC's power state. The following values are defined:                                                                                     |

|        |                     | 0 = State D0                                                                                                                                                                                   |

|        |                     | ■ 1 = State D1                                                                                                                                                                                 |

|        |                     | ■ 2 = State D2                                                                                                                                                                                 |

|        |                     | ■ 3 = State D3                                                                                                                                                                                 |

|        |                     | If this bit is set to a nonzero value, the NIC does not respond to PCI I/O or memory cycles, nor is it able to generate PCI bus master cycles.                                                 |

| [8]    | pmeEn               | When this read/write bit is set, the NIC is allowed to report wake-up events on the PME# signal. The specific events that can generate wake-up are defined by the PowerMgmtEvent I/O register. |

| [12:9] | dataSelect          | These read/write bits select which power consumption value is to be reported when reading the PowerConsumption register.                                                                       |

|        |                     | The NIC currently supports values of 0x0 to 0x7h, based on the following table:                                                                                                                |

|        | Value in dataSelect | Data Reported                                                                                                                                                                                  |

|        | 0,4                 | D0 Power Consumed/Dissipated                                                                                                                                                                   |

|        | 1,5                 | D1 Power Consumed/Dissipated                                                                                                                                                                   |

|        | 2,6                 | D2 Power Consumed/Dissipated                                                                                                                                                                   |

|        | 3,7                 | D3 Power Consumed/Dissipated                                                                                                                                                                   |

|        | 8-15                | not supported                                                                                                                                                                                  |

#### PowerMgmtCtrl Bit Descriptions (continued)

| Bit     | Name      | Description                                                                                                                                                           |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [14:13] | dataScale | These read/write bits define the scaling factor associated with the PowerConsumption register.                                                                        |

|         |           | These bits always read 0x10b, meaning that the value in the PowerConsumption register should be multiplied by 0.01, giving a result in units of Watts from 0 to 2.56. |

| [15]    | pmeStatus | This read/clear bit is set to indicate a wake-up event has occurred. This bit is set regardless of the value in pmeEn.                                                |

|         |           | Writing a one to this bit clears it. Writing a zero has no effect.                                                                                                    |

#### **PowerMgmtEvent**

| Synopsis | Allows control over power management event generation. |

|----------|--------------------------------------------------------|

| Туре     | Read/write                                             |

| Size     | 16 bits                                                |

| Window   | 7                                                      |

| Offset   | C                                                      |

The PowerMgmtEvent register contains enable bits to control which types of events can generate a wake-up event in the host system. It also contains status bits that indicate what specific events have occurred.

The PowerMgmtEvent register is cleared by a LVDRst.

The enable bits in this register determine what types of events can cause the NIC to generate a wake-up event (interrupt) on the PCI bus. All enable bits are qualified with the pmeEn bit in the PowerMgmtCtrl configuration register. If the pmeEn bit is clear, then wake-up generation is disabled and these bits are ignored.

The event bits indicate that an actual wake-up event has occurred. These bits are masked by their corresponding enable bits above. If the enable bit is set, then the event bit can never become set. Once set, the event bits are cleared by a read to the PowerMamtEvent register.

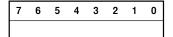

#### PowerMgmtEvent Register Format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 0  | 0  |    |   |   |   |   |   |   |   |   |   |   |

#### PowerMgmtEvent Bit Descriptions

| Bit | Name            | Description                                                                                                                                       |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| [0] | wakeupPktEnable | This read/write bit, when set, causes the NIC to generate a wake-up event due to wake-up packet reception.                                        |

| [1] | magicPktEnable  | This read/write bit, when set, enables the NIC to generate a wake-up event due to a Magic Packet frame reception.                                 |

| [2] | linkEventEnable | This read/write bit, when set, enables the NIC to generate a wake-up event due to a change in link status (cable is disconnected or reconnected). |

#### PowerMgmtEvent Bit Descriptions (continued)

| Bit  | Name              | Description                                                                                                                                                                                                                       |  |  |  |  |  |  |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [3]  | wakeOnTimerEnable | This read/write bit, when set, enables the NIC to general a wake-up event due to the WakeOnTimer register expiring.                                                                                                               |  |  |  |  |  |  |

| [4]  | wakeupPktEvent    | This bit indicates that a wake-up event (which meets the reception criteria set by software) has been received.                                                                                                                   |  |  |  |  |  |  |

| [5]  | magicPktEvent     | This bit indicates that a Magic Packet frame has been received.                                                                                                                                                                   |  |  |  |  |  |  |

| [6]  | linkEvent         | This bit indicates that a link status event has occurred.                                                                                                                                                                         |  |  |  |  |  |  |

| [7]  | wakeOnTimerEvent  | This bit indicates that a wake-on-timer status event has occurred.                                                                                                                                                                |  |  |  |  |  |  |

| [8]  | kapEn             | This read/write bit, when set, places the transmit FIFO in the keep-alive mode. The KeepAliveTimer starts running, and the NIC sends keep-alive packets as programmed.                                                            |  |  |  |  |  |  |

| [9]  | startKap          | This read/write bit, when set, allows the keep-alive function to start, if the kapEn bit is set.                                                                                                                                  |  |  |  |  |  |  |

| [10] | linkWpToKaEn      | Link wake-up packet to keep-alive packet. Whenever a receive packet matches a wake-up pattern with a non-zerotrigSel value, a keep-alive packet that has the same trigSel value is transmitted, and the PMEN pin is not asserted. |  |  |  |  |  |  |

#### Remote Wake-Up

The 3C90xC NIC supports Remote Wake-Up, the ability to remotely power on a PC that is in standby or suspend mode.

The NIC can generate a wake-up signal to the system as a result of any of the three standard wake-up events defined by the *Device Class Power Management Reference Specification* — *Network Device Class*:

- Wake-up packet reception

- Magic Packet reception

- Change in link state

The NIC can also cause a system wake-up based on two additional events:

- Wake-on-Timer

- Wake-On-SMB

The PowerMgmtEvent register gives the driver control over which of these events is passed to the system. Wake-up events are signaled over the PCI bus using the PME# pin.

#### Wake-up Packets

The NIC can signal wake-up when the NIC receives an "interesting" packet from another station. Driver software defines interesting packets by downloading a set of frame patterns to the transmit FIFO before placing the NIC in a power-down state. Once the NIC is powered down, it compares receive packets with the frame patterns. Wake-up is signaled when a packet is received that matches a frame pattern and also passes the filter set in the RxFilter register.

A signature-matching technique allows the NIC to recognize wake-up packets. The frame patterns specify which bytes in the incoming packets are to be examined. A CRC is calculated over these bytes and compared with a CRC value supplied in the frame pattern. This matching technique may result in false wake-ups being reported to the system.

Packet wake-up is controlled by the wakeupPktEnable bit in the PowerMgmtEvent register. This can occur in any power state (D0 to D3); however, normal transmit and receive functions do not operate properly when this function is enabled. When the NIC detects a wake-up packet, it signals a wake-up event on PME# (if PME# assertion is enabled), and sets the wakeupPktEvent bit in PowerMgmtEvent.

#### **Downloading Wake-up Frame Patterns**

Drivers download frame patterns to the transmit FIFO in a single "pseudo packet":

- 1 Issue a TxReset command (to reset the FIFO pointers and prevent transmission).

- 2 Prepare a DPD that points to a single data buffer.

The buffer contains one or more frame patterns, placed contiguously. The transmit FIFO size limits the number of frame patterns. The DnFragLen DPD entry must exactly equal the sum of the frame pattern bytes.

- 3 Set the rndupDefeat bit in the Frame Start Header DPD entry to prevent rounding up of the packet size.

- 4 Write the DPD address to the DnListPtr register to download the packet.

#### **Wake-up Frame Patterns**

Each wake-up frame pattern contains the following:

- One or more byte offset/byte count pairs—The byte offset indicates the number of packet bytes to be skipped in order to reach the next group of bytes to be included in the CRC calculation. The byte count indicates the number of bytes in the next group to be included in the CRC calculation.

- End-of-pattern symbol—This byte value (00) indicates the end of the pattern for that wake-up frame.

- Four-byte CRC value—This CRC value uses the same polynomial as the Ethernet MAC CRC.

The frame patterns are encoded as follows: The byte offset/byte count values are contained in a single byte. Bits [7:4] contain the byte offset value, and bits [3:0] contain the byte count. The byte offset and byte count can take on a value of 0 to 14d. A byte offset or byte count value of 15d indicates that it has an extended value: this value occupies eight bits and is contained in the next pattern byte. If both the byte offset and the byte count values are 15d, the next byte is the extended byte offset, and the byte after that is the extended byte count.

Offset/count bytes occur in the pattern until terminated by a zero byte, which indicates the end of pattern for that wake-up frame. Following the end of pattern are four bytes of CRC value. If there is another wake-up frame pattern, then it immediately follows the CRC value.

As an example, the following is the pattern to be downloaded into the transmit FIFO for the ARP wake-up frame shown in Appendix A of the *Network Device Class Specification*:

```

c2

// byte offset = c, byte count = 2

71

// byte offset = 7, byte count = 1

f4

// byte offset = extended, byte count = 4

10

// byte offset = 10h

00

// end of pattern

f3

// first byte of CRC

19

// second byte of CRC

// third byte of CRC

08

d7

// fourth byte of CRC

```

#### Magic Packet Technology

The NIC can signal wake-up when it receives a Magic Packet frame from another station.

The Magic Packet technology, developed by Advanced Micro Devices, allows remote wake-up of a sleeping station on a network. The technology involves sending a special packet to the sleeping station. Once a station has been placed in Magic Packet mode and put to sleep, it scans all incoming packets addressed to it for a specific data sequence.

The data sequence consists of 16 duplications of the Ethernet MAC address of the station, with no breaks or interruptions. This sequence can be located anywhere within the packet, but must be preceded by a synchronization stream. The synchronization stream is defined as six bytes of FFh.

The device also accepts a broadcast frame as long as the 16 duplications of the MAC address match the address of the machine to be awakened. If the MAC address for a particular node on the network was 11:22:33:44:55:66, then the LAN controller would be scanning for the following data sequence:

Destination\_Address Source\_Address {Miscellaneous} FF FF FF FF FF FF 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 11 22 33 44 55 66 {Miscellaneous} CRC